This article first introduces the use of automated synthesis tools to complete the optimization of HDTV chip design at the coding and synthesis stage. Since the quality of the Verilog code directly affects the combined results, the comprehensive requirements should be taken into account during the design of the code. Secondly, it introduces the characteristics and structure of the HDTV chip, and focuses on the complicated structure and solution of the HDTV chip. Finally, it introduces how to optimize the design of the HDTV chip with the integrated tool Design Compiler, reducing the delay from -0.94 to 0.11.

VerilogHDL comprehensive design

1 clock arrangement

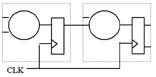

Use a single-clock signal triggered by a rising edge and try not to use the mixed-trigger clock signal. Because the clock cycle is a critical issue in the timing analysis process, it also affects the frequency of the clock. The use of a simple clock structure facilitates the analysis and maintenance of the clock signal, avoiding the addition of buffers to the clock signal, and also facilitates better overall results. Figure 1 shows the single-clock signal structure triggered by the rising edge.

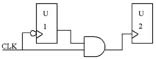

Try to avoid using a gated clock. Clock gating circuits are often associated with process and timing, and erroneous timing relationships can cause erroneous clock and pulse interference. The skew of the clock causes confusion in the hold TIme, as shown in Figure 2. In addition, gated clocks can degrade the testability of the design.

Also, avoid using internal parasitic clocks and parasitic resets. The parasitic clock cannot be used as part of the scan chain, so the testability of the design is degraded, and the design of the integrated constraint is more difficult. Only some low-power designs require a gated clock. Be careful to use a clock or reset circuit as a discrete module in the top-level module.

2 integrated code

The use of synthesizable code improves circuit testability, simplifies static timing analysis, and aligns gate-level circuitry with initial register-level code functionality.

The use of registers instead of combinatorial logic feedback avoids the use of latches (Latches). Registers are favored by sequential logic to maintain consistency and comprehensive correctness. The reset signal is used in the design to initialize the register signal. Do not use the iniTIal statement to initialize the signal in Verilog.

In each always block, specify a complete list of sensitive signals. If you do not specify a complete sensitive signal, the behavioral front-end synthesis and back-end integrated netlist results will not match. The synthesis tool will give a warning when designing the design. Adding extra sensitive signals will slow down the simulation. In addition, pay attention to the problem of blocking assignment and non-blocking assignment. Obstructive assignment is generally used in sequential circuits.

The Case statement is equivalent to a single-layer multiplexer; the If-then-else statement is equivalent to a cascaded combined multiplexer. A single multiplexer will be faster, so a case statement is usually recommended. Avoid using full-case and parallel_case, which can cause differences in code interpretation during simulation and synthesis.

The code that writes the sequential logic includes a state machine and a time-series process that improves the readability of the code by generating complex internal intermediate variables using the assign statement outside the process. Use the define statement to define the state vector. Placing finite state machines and non-finite state machines in different modules facilitates synthesis.

Do not use any delay constants in RTL code. The amount of delay not only causes inaccuracies in some environments, but also results in inconsistent simulation and synthesis results, disrupting the optimization of the RTL emulator code.

The Samsung Note 8 Battery has a capacity of 3300mAh,battery type is lithium polymer,it comes with a special chip to protect your smart phone from over heating,short-circuit,over charging and over discharging.This replacement Phone Battery will 100% compatible with your Samsung Note 8.We also have other Samsung series batteries,such as Samung A8 battery,Samsung A9 Battery,Samsung S8 Battery,Samsung S8 Plus Battery, Samsung S9 Battery etc.Welcome your trial orders to test our quality and service.

Samsung Note 8 Battery

Samsung Note 8 Battery,Battery For Samsung Note 8,Galaxy Note 8 Battery,Samsung Galaxy Note 8 Battery

Shenzhen Hequanqingnuo Electronic Technology Co., Ltd. , https://www.hqqnbattery.com